# アナログ・デジタル混載システムLSIの研究

## - 携帯機器用チャージポンプ電源回路の高性能化 -

## 小林 春夫

群馬大学工学部電気電子工学科 〒 376-8515 群馬県桐生市天神町 1-5-1 Tel: 0277-30-1788 Fax: 0277-30-1707 e-mail:k\_haruo@el.gunma-u.ac.jp

要約 - 携帯機器に使用するための高効率・低ノイズでコイルを使用いないチャージポンプ電源回路の高性能化に向けて次のことを行ったので報告する。

- (i) 先に提案したブートストラップ・ゲート転送スイッチを用いたチャージポンプ回路構成を VDEC 1.2 $\mu$ mCMOSプロセスで試作し、そのチップの測定評価を行った。

- (ii) 負荷電流の変動に応じてクロック周波数制御することで昇圧型チャージポンプ回路を高効率化する方式を提案し、そのクロック周波数制御回路の構成を検討した。

キーワード: チャージポンプ、DC-DC変換器、電源回路

#### I. 研究背景

近年の携帯電話、PDA、DSC 等の携帯機器では駆動時 間を延ばすための低消費電力化がますます進んでいく一 方、カメラ付きなどの機能の高性能化によって、高効率 な高電圧および低電圧、大電流出力電源の必要性が高まっ ている。これらの要求を満たすためには、ひとつの外部 電源からチップ内部で多種類の電源電圧を高効率・低ノ イズで生成する電源回路が必要となってくる。このため のスイッチング・レギュレータ回路は非常に高効率である が、外付けのコイルを必要としスイッチング・ノイズを発 生するという問題がある。一方、チャージポンプ回路は 容量とスイッチでオンチップで実現でき発生ノイズが小 さいというメリットがある反面、既存の回路では昇圧効 率が悪く電流負荷出力が低かった。そこで著者らは大電 流出力、高効率チャージポンプ電源回路の開発を行った [2, 3, 4]。ここでは我々の先の研究[5, 6, 7]に基づき、次 のような別の観点からチャージポンプ電源回路の高性能 化に関して検討を行った。

(i) [2, 3, 4] では昇圧した内部ノード電位を転送スイッチのゲートにフードバックしているが、ここでは [5] で提案した容量を用いたブートストラップ方式を改良してチップ実現しその動作を検証した。チャージポンプ回路は入力電源電圧より高い電圧を発生するため、シミュレーションだけでなくチップの試作・測定による動作検証は必須である。

(ii) [6, 7] で導出したチャージポンプ回路の効率式に基づき、負荷電流変動に応じてクロック周波数を自動制御する機構を設けることで高効率化する方式を提案しその回路構成を検討した。

II. ブートストラップ転送スイッチ使用のチャージポンプ 回路の設計と測定

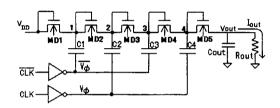

## 2.1 オリジナル Dickson チャージポンプ回路

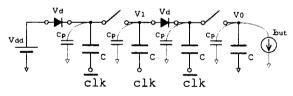

図 1 に Dickson により提案されたチャージポンプ回路を示す [1]。ドレインとゲートがダイオード接続された NMOS 電荷転送スイッチ (MD1~MD5) を通して振幅が電源電圧  $V_{ad}$  である相補的クロック CLK、 $\overline{CLK}$ (ポンプ・クロック)により電荷が一つの方向のみ押し出される。カップリング・コンデンサー  $C_1 \sim C_4$  の容量の値は等しく C とする。電荷が二つのクロック信号の動作により持上げられ、ダイオード接続 NMOS を通して容量に流れ込み、各ノードを昇圧する。しかしながらこの方式は各電荷転送スイッチにおいて NMOS スレショルド電圧分の電圧降下が生じ昇圧電圧、効率が劣化するという問題点をもっている。

#### 2.2 提案チャージポンプ回路

このオリジナルの Dickson チャージポンプ回路の問題を解決するために著者らは [5] でブートストラップ転送スイッチを用いる方式を提案した。ここではその回路に少し改良を加えた。その回路は次の特徴を持つ。

高効率: 提案した回路の出力電圧は、従来式回路に比べて少ない段数でより高い電圧を供給する事ができるので、 高効率となる。

低電圧動作可能: 提案した回路は Dickson チャージポンプ回路が動作可能の必要条件 [5] に制限されないため、低電源電圧でも動作する事が可能である。

なお、使用 CMOS プロセスは *N*-ウェルプロセスを前提とする。*N*-ウェルプロセスは多くのデジタル CMOS プロセスで用いられ、また PMOS の基板電圧を制御する事が可能なので、高い正の電圧を発生するのに適している。一方、*P*-ウェル プロセスは負の電圧を発生するには適し

ている。トリプル-ウェルプロセスは上述した2つのプロセスより適用幅は広いがコスト高になる。

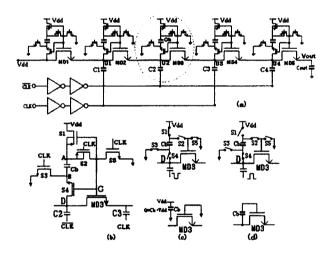

**A. 提案回路 1:** 図 2 (a) に提案した 4 段チャージポンプ 回路 1 の構成を示す。その動作は以下のようになる。

## 電荷転送スイッチ MD3 が OFF 状態 (図 2(c)):

ノード D の電圧が Low の場合、NMOS スイッチ M の ゲートがグランドに接続され、MD3 が OFF する。容量  $C_b$  には  $C_bV_{dd}$  の電荷がチャージされる。

## 電荷転送スイッチ MD3 が ON 状態 (図 2(d)):

ノード D の電圧が High の場合、MD3 のドレインとゲートは  $C_b$  の両端に接続され、M のドレイン-ゲート間電圧は  $V_{dd}$  となり、 MD3 が ON する。

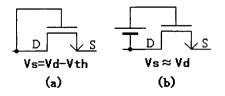

電荷転送スイッチ MD3 が ON 状態のとき、MD3 のドレインとゲート間電圧が  $V_{dd}$  であるため、定常状態ではドレイン-ソース間の電圧ドロップほぼゼロである (図 3(b))。従って、従来式の Dickson チャージポンプ回路におけるスレショルド電圧ドロップの問題 (図 3(a)) が解決される。 また、ダイオード接続された MOS スイッチ (図 3(a)) に比べて提案した回路 (図 3(b)) では電荷転送スイッチ MD3 の ON 抵抗が十分に小さくなっている。

図 2(b) に示した提案回路 1 での動作を以下に記す。各 1 一ドの電位は  $V_{dd}$  以上になることに注意する必要がある。

- 電荷転送スイッチ OFF 状態において、S1,S3 と S5 が ON で、S2 と S4 が OFF である。電荷転送スイッチ ON 状態において、S2 と S4 が ON で、S1,S3 と S5 が OFF である。

- スイッチ S1 は PMOS デバイスで実現するが、ノード A の電圧は電源電圧  $V_{dd}$  より高くなる場合があるので、S1 のボディをノード A、ゲートをノード G に接続する。電 荷転送スイッチ ON 状態において、CLK が Low で、S2 が ON になる。従って、S1 のゲート電圧とソース電圧は等しくなるので、S1 が OFF になる。一方、電荷転送スイッチ OFF 状態において、CLK が High で、S1 のゲート電圧がゼロになり、S1 が ON になる。

- ノードAの電圧は常にノードGの電位より高いので、PMOSスイッチS2のボディはノードAに接続する。

- NMOS スイッチ S4 のゲートをノード G に接続する。電荷転送スイッチ ON 状態において、CLK が Low で、S4 のゲート電圧は  $V_B+V_{dd}$  であるので、S4 が ON になる。一方、電荷転送スイッチ OFF 状態において、CLK が High で、S4 のゲート電圧がゼロになり、S4 が OFF になる。

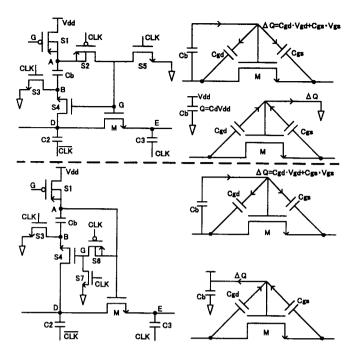

- B. 提案回路 2: 図 2 で示す提案回路 1 において、ON 抵抗を小さくするため電荷転送スイッチ M のサイズは他の MOSFET スイッチに比べて非常に大きいので、そのゲート容量  $(C_{qs},C_{qd})$  も比較的に大きくなる。従って、次の

ようなそのゲート容量を充放電するためのダイナミック 消費電力を無視する事が出来なくなる。

- ON 状態において、ノード G の電圧が高くなり、ノード G に接続する寄生容量は充電される。

- OFF 状態において、NMOS スイッチ *M* のゲートが グランドに接続され、寄生容量に溜まった電荷がグラン ドに放電される。

- この電荷の充放電はエネルギーの浪費(消費電力増加)だけでなくポンプ・ゲインにも低減させてしまうので、この問題を解決する改良回路を図 4 に提案する。ここでは電荷転送スイッチ M のゲートをノード A に接続しており、また動作は次のようになる。

- M が ON 状態: S6 と S4 が ON で、S1,S3 と S7 が OFF である。NMOS スイッチ M の寄生容量  $C_{gs}$  と  $C_{gd}$  が充電される。

- M が OFF 状態:  $S6 \ge S4$  が OFF で、 $S1, S3 \ge S7$  が ON である。

$C_{gs}$  と  $C_{gd}$  の電荷に注目すると、NMOS スイッチ M のゲートはノード A に接続されているので、電荷はグランドではなく、再び  $C_b$  に注入する事になり、電荷を空費する事が回避される。また、M が OFF 状態のとき M のゲート電位はゼロでなく  $V_{dd}$  であるが、ノード D と E の電圧は  $V_{dd}$  に等しい或いは  $V_{dd}$  より高く、M のゲートソース間電圧がゼロより小さいので M が OFF になる事が保証される。

#### 2.3 チャージポンプ回路の SPICE シミュレーション

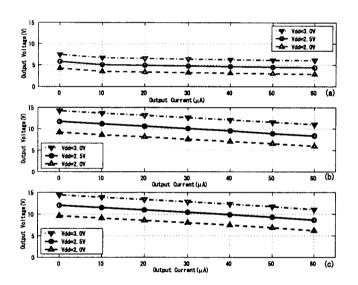

4段 Dickson チャージ・ポンプ回路、提案回路 1、提案回路 2の SPICE シミュレーションを行ない動作を確認した。図 5 に  $V_{out}$  vs.  $I_{out}$  特性の比較結果を示す。シミュレーション条件は C=15pF、 $C_{out}=30pF$ 、f=5MHzで、 $V_{dd}$  は 2.0 V、2.5 V、3.0 V である。提案回路 2 の出力電圧が最も高い事がわかる。例えば、 $V_{dd}=3.0$  V、 $I_{out}=20\mu$  の場合、Dickson チャージ・ポンプ回路の出力電圧が 6.5 V であるが、提案回路 1 の出力電圧が 13.1 V、提案回路 2 の出力電圧が 13.4 V である。

## 2.4 提案チャージポンプ回路のレイアウト、チップ実現

提案した回路の動作機能を検証するために、提案回路 1、2のレイアウト設計を行いチップ試作を行った。使用プロセスは VDEC 経由で Motorola 社が提供する  $1.2~\mu m$ CMOSプロセスである。図 6 に提案回路 1、2 のチップ写真を示す。それぞれの図で上部に 2 個、下部に 3 個の正方形は2pF のブートストラップ用容量  $C_b$  で、中央部が電荷転送スイッチの NMOS とブートストラップ転送スイッチである。また、カップリング容量  $C_1-C_4$  と出力容量  $C_{out}$  は外付けとした。

#### 2.5 チャージポンプ回路チップの測定

オリジナルの Dickson チャージポンプ回路と提案回路 1 のチップの測定評価を行った。測定機器は、直流電源: AD-VANTEST 社 81110A、パルス発生器: Agilent 社 R6243 等を使用した。

図 7 に入力電圧、クロック振幅  $V_{dd}$  を変化させたときの Dickson チャージポンプ回路と提案回路 1 の出力電圧の測定結果を示す。どちらの回路も C=100pF、 $C_{out}=200pF$ 、 $C_b=2pF$  で、クロック周波数は 1MHz で動作させた。提案回路 1 のほうがより高く昇圧していることがわかる。例えば、Vdd=1.0V の場合、Dickson チャージポンプ回路の出力電圧は 1.8V であるが、提案回路 1 は 3.6V である。

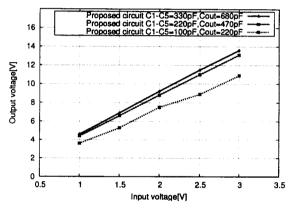

図 8 に提案回路 1 のチップの外付け容量の値を変えて出力電圧を測定した結果を示す。(i) C=100pF,  $C_{out}=200pF$ , (ii) C=220pF,  $C_{out}=470pF$ , (iii) C=330pF,  $C_{out}=680pF$  の 3 つの場合で測定した。いずれの場合も  $C_b=2pF$  で、クロック周波数は 1MHz で動作させた。C、 $C_{out}$  の容量を大きくしたほうが昇圧し、より理論値に近づいていることがわかる。例えば、Vdd=1.0V のとき出力電圧は (i) の場合は 3.6V、(ii) はの場合は 4.4V、(iii) の場合は 4.6V である。これは容量を大きくすることで寄生容量の影響が小さくなったためと考えられる。

# III. クロック周波数の自動制御によるチャージポンプ回路の高効率化

#### 3.1 チャージポンプ回路の理論効率

図 9 に示す回路の非理想特性 ( $V_d$ : スイッチ ON 時の電圧降下、 $C_p$ : 各ノードの寄生容量、 $I_{out}$ : 負荷電流) を考慮した N 段チャージポンプ回路の効率  $\eta_p$  を次のように導出した。[6,7]。

$$\eta_p := 1 - \frac{N\alpha + 2(N+1)(1+\alpha)\beta x + 4Nx^2}{N\alpha + 2\gamma x}$$

(1)

$$X := \frac{TI_{out}}{CV_{dd}}, \qquad \alpha := \frac{C_p}{C}, \qquad \beta := \frac{V_d}{V_{dd}}.$$

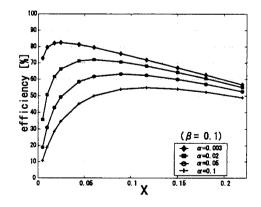

ここで、x,  $\alpha$ ,  $\beta$ ,  $\gamma$  は無次元の定数、 $\gamma:=N+1+\alpha$ 、T はクロックの周期である。図 10 に、 3 段チャージポンプ 回路で  $\alpha=0.003,0.02,0.05,0.1$ 、 $\beta=0.1$  の場合の式 (1) から数値計算した X に対する効率  $\eta_p$  を示す。

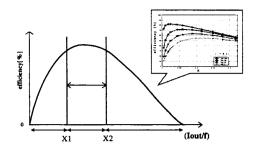

図 11 は図 10 を模式的に表わしたものであるが、このグラフで、横軸が [負荷電流  $I_{out}$ /クロック周波数 f] となっている (f:=1/T)。今回提案するのは、負荷電流  $I_{out}$  の変動に伴い  $I_{out}$ /f を常に X1 と X2 の間になるようにクロック周波数 f を自動制御し、チャージポンプを常に最大効率付近で動作させる方式である。例えば、 $I_{out}$  が小さいときは f を小さくすることにより  $I_{out}$ /f を一定に保ち、高効率動作範囲で動作させる。。

#### 3.2 提案するクロック周波数制御回路の構成と動作

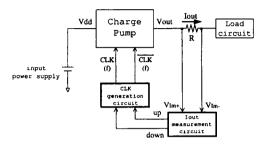

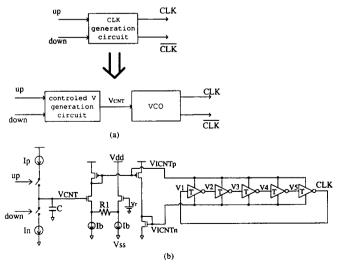

A. 全体構成: 図 12 に提案するクロック周波数制御回路 の全体図を示す。チャージポンプ出力電流測定回路 (Iout measurement circuit)、クロック生成回路 (CLK generation circuit) から成る。"Load circuit"は後段の負荷回路である。Vout は、チャージポンプの出力電圧であり、また後段回路の入力電源電圧でもある。Iout は、後段回路の動作状態に伴い変動するが、。この Iout を出力電流測定回路で検出し、次に Iout の変動に伴いチャージポンプのクロック周波数をクロック生成回路により自動調節する。このようにすることでチャージポンプを効率を常に最大付近で動作させることができる。

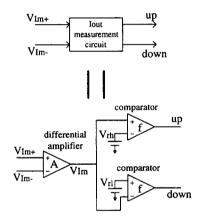

B. 出力電流測定回路 図 13 に出力電流測定回路を示す。 差動ーシングルエンド変換回路と2つのコンパレータ2つ から成る。入力 Vim+,Vim-の差である Vim と基準電圧

Vrh, Vrl (Vrl < Vrh) を比較し、ups 信号と down 信号を生成する。例えば、Vim < Vrl のときは、下のコンパレータで検出され down=1 となる。また、Vim > Vrh のときは、上のコンパレータで検出され up=1 となる。この up, down 信号をクロック生成回路に入力し、クロック周波数を制御する。

C. クロック生成回路: 図 14 にクロック生成回路を示す。制御電圧発生回路と VCO (Voltage Controlled Oscillator) から成り、また VCO 回路はリング発振器で構成できる。制御電圧発生回路に up,down の信号を入力し制御電圧 Vcnt を生成する。Vcnt は VCO に入力され発振周波数(クロック周波数) f が発生される。

これらの回路の基本動作を SPICE シミュレーションで 確認した。

## IV. まとめと今後の課題

- (i) ブートストラップ・ゲート転送スイッチを用いたチャージポンプ回路構成を提案し、チップで実現したものを測定評価した。Dickson チャージポンプ回路より高く昇圧することが確認できた。

- (ii) 負荷電流の変動に応じてクロック周波数制御することで昇圧型チャージポンプ回路を高効率化する方式を提案した。また、そのクロック周波数制御回路の構成を検討した。

また、今後の大きな研究テーマとして、デジタルのプロセッサの低消費電力化等のために需要の大きい高効率な大電流出力降圧型チャージポンプ電源回路の開発がある。付録に取り組んでいる回路トポロジを記す。

謝辞 本研究は、(財) 高柳記念電子科学技術振興財団の 平成13年度研究助成を受けて行われた。ここに深く感 謝の意を表する。また有意義な技術討論をいただいた三 洋電機の方々に謝意を表する。本チップ試作は東京大学大 規模集積システム設計教育研究センターを通し オンセミコンダクター (株)、日本モトローラ (株)、HOYA(株)、および京セラ (株) の協力で行われた。

#### 参考文献

- [1] J. F. Dickson, "On-Chip High-Voltage Generation in NMOS Integrated Circuits Using an Improved Voltage Multiplier Technique," *IEEE J. Solid-State Circuits*, vol.11, pp.374-378 (June 1976).

- [2] T. Myono, S. Kawai, A. Uemoto, T. Iizima, and H. Kobayashi, "Highly Efficient Charge-Pump Circuits with Large Output Current Load for Mobile Equipment Applications," *IEICE Trans. Electron*, vol.E84-C, no.10, pp.1602-1611 (Oct.2001).

- [3] T. Myono, T. Suzuki, A. Uemoto, S. Kawai, T. Iizima, N. Kuroiwa, and H. Kobayashi, "High-Efficiency Charge-Pump Circuits which use a 0.5Vdd-Step Pumping Method," *IEICE Trans. on Fundamentals*, vol. E86-A, no. 2, pp.371-380 (Feb. 2003).

- [4] T. Myono, Y. Onaya, K. Kashiwase, H. Kobayashi, T. Nishi, K. Kobayashi, T. Suzuki, K. Henmi, "Reducing Startup-time Inrush Current in Charge Pump Circuits," *IEICE Trans. on Fundamentals*, E87-A, no. 4, (April. 2004).

- [5] H. San, H. Kobayashi, T. Myono, T. Iijima and N. Kuroiwa, "Highly-Efficient Low-Voltage-Operation Charge Pump Circuits Using Bootstrapped Gate Transfer Switches", 電気学会論文誌 C (電子・情報・システム部門誌), vol.120-C, No.10, pp.1339-1345 (Oct. 2000).

- [6] K. Kashiwase, H. Kobayashi, N. Kuroiwa, N. Hayasaka, S. Inaba, T. Myono, T. Suzuki, T. Iijima, S. Kawai, "Dynamics of Parallel-Type and Serial-Type Charge Pump Circuits for High Voltage Generation", 2002 IEEJ International Analog VLSI Workshop, pp.14-19, Singapore (Sept. 2002).

- [7] K. Kashiwase, H. Kobayashi, N. Kuroiwa, N. Hayasaka, T. Myono, T. Suzuki, T. Iijima, S. Kawai, "Dynamics of Dickson Charge Pump Circuit," 第15回 回路とシステム(軽井沢) ワークショップ, pp.375-380 (April 2002).

- [8] J. T. Wu and K. L. Chang, "MOS Charge Pumps for Low-Voltage Operation," *IEEE J. Solid-State Circuits*, vol.33, no.4, pp.592-597 (April 1998).

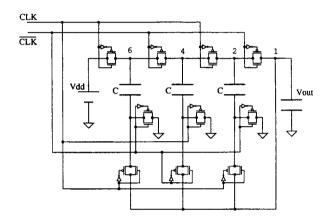

#### 付録: 降圧型 Dickson チャージポンプ回路

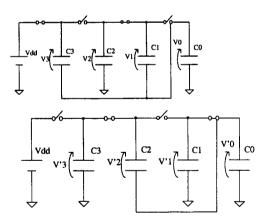

Dickson 型での降圧チャージポンプ回路の構成を提案する。図 16 に提案する降圧型 Dickson チャージポンプ回路の構成、図 17 にその動作を示す。この回路は入力電圧 Vdd から Vdd/4 を生成・出力する回路である。従来のスイッチド・キャパシタ型降圧回路と同様に CMOS スイッチの切り替えによって動作する。クロック信号により CMOS スイッチを on・off し、定常状態でノード 6 は 3Vdd/4、ノード 4 は 2Vdd/4、ノード 1,2 は Vdd/4 に降圧する。昇圧型 Dickson チャージポンプ回路では、カップリング容量を振幅電圧一定の Vdd で駆動しているが、内部ノード電圧をフィードバックさせて用いている。

動作を電荷保存則を用いて式で確認すると、図17の上側の状態で次のようになる。

$Vdd = V3 - V1 + V2, \quad -V1 + V2 = V0.$

一方図17の下側の状態で次のようになる。

$$V'3 = V'2 + V'1$$

,  $V'1 = V'0$ .

定常状態のとき電荷の移動がないので、

V0 = V'0, V1 = V'1, V2 = V'2, V3 = V'3 が成り立つ。これらの式より電源電圧 Vdd のとき、

$$V0 = V1 = \frac{1}{4}Vdd$$

,  $V2 = \frac{2}{4}Vdd$ ,  $V3 = \frac{3}{4}Vdd$

となる。SPICEシミュレーションにより定常状態での出力 電圧のノイズ、リップルが小さいことが確認できている。

Fig.1: 4 段 Dickson チャージポンプ回路 [1].

Fig.2: 提案チャージポンプ回路 1. (a) 全体の回路図 (4 段の場合). (b) ブートストラップ・ゲート転送スイッチ. (c) スイッチ OFF 状態. (d) スイッチ ON 状態.

Fig.3: 転送スイッチの ON 状態特性. (a) Dickson チャージポンプ回路. (b) 提案するチャージポンプ回路.

Fig.4: 提案チャージポンプ回路 2. 電荷転送スイッチ M のゲートへの電荷の充放電のロスが少ない構成である.

Fig.5:  $V_{out}$  vs.  $I_{out}$  特性の SPICE シミュレーション比較結果. (a) Dickson チャージ・ポンプ回路. (b) 提案回路 1. (c) 提案回路 2.

Fig.21: 提案チャージポンプ回路 1 (左) と回路 2 (右) のチップ写真.

Fig.7: 4段 Dickson チャージポンプ回路と提案回路 1 の入力電  $\mathbb{E} V_{dd}$  に対する出力電圧  $V_{out}$  の測定結果.

Fig.8: 様々なポンプ容量 C、出力容量  $C_{out}$  値に対する提案回路 1 の入力電圧  $V_{out}$  に対する出力電圧  $V_{out}$  の測定結果.

Fig.9: 回路の非理想特性(スイッチの電圧ドロップ  $V_d$ 、出力電流  $I_{out}$ 、寄生容量  $C_p$ )を考慮した Dickson チャージポンプ回路.

Fig.10: 図 9 に示した 3 段 Dickson チャージポンプ回路の理論 効率. 式 (1) から数値計算で得た.

Fig.11: Dickson チャージポンプ回路の理論効率の模式図. X1 < (Iout/f) < X2 になるようにクロック周波数を制御する.

Fig.12: 提案するクロック周波数を自動制御する回路の全体図.

Fig.13: 出力電流測定回路全体図.

Fig.14: (a) クロック生成回路ブロック図. (b) クロック生成回路図.

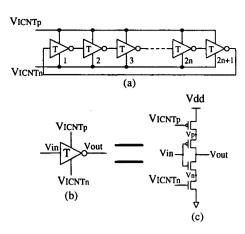

Fig.15: (a) リング発振器の全体図. (b) インバータのブロック図. (c) インバータ回路. バイアス電圧  $V_{ICNT_p}$ ,  $V_{ICNT_n}$  でインバータ回路の遅延時間が制御される。

Fig.16: 提案降圧型 Dickson チャージポンプ回路の構成.

Fig.17: 提案降圧型 Dickson チャージポンプ回路の動作. 上図と下図の状態をクロックの High, Low に応じて繰り返す.